Deep reactive-ion etching

This article needs additional citations for verification. (December 2009) |

Deep reactive-ion etching (DRIE) is a special subclass of reactive-ion etching (RIE). It enables highly anisotropic etch process used to create deep penetration, steep-sided holes and trenches in wafers/substrates, typically with high aspect ratios. It was developed for microelectromechanical systems (MEMS), which require these features, but is also used to excavate trenches for high-density capacitors for DRAM and more recently for creating through-silicon vias (TSVs) in advanced 3D wafer level packaging technology.

In DRIE, the substrate is placed inside a reactor, and several gases are introduced. A plasma is struck in the gas mixture which breaks the gas molecules into ions. The ions are accelerated towards, and react with the surface of the material being etched, forming another gaseous element. This is known as the chemical part of the reactive ion etching. There is also a physical part, if ions have enough energy, they can knock atoms out of the material to be etched without chemical reaction.

There are two main technologies for high-rate DRIE: cryogenic and Bosch, although the Bosch process is the only recognised production technique. Both Bosch and cryogenic processes can fabricate 90° (truly vertical) walls, but often the walls are slightly tapered, e.g. 88° ("reentrant") or 92° ("retrograde").

Another mechanism is sidewall passivation: SiOxFy functional groups (which originate from sulphur hexafluoride and oxygen etch gases) condense on the sidewalls, and protect them from lateral etching. As a combination of these processes, deep vertical structures can be made.

Cryogenic process

[edit]In cryogenic-DRIE, the wafer is chilled to −110 °C (163 K). The low temperature slows down the chemical reaction that produces isotropic etching. However, ions continue to bombard upward-facing surfaces and etch them away. This process produces trenches with highly vertical sidewalls. The primary issues with cryo-DRIE is that the standard masks on substrates crack under the extreme cold, plus etch by-products have a tendency of depositing on the nearest cold surface, i.e. the substrate or electrode.

Bosch process

[edit]

The Bosch process, named after the German company Robert Bosch GmbH which patented the process,[1][2][3][4][5][6] also known as pulsed or time-multiplexed etching, alternates repeatedly between two modes to achieve nearly vertical structures:

- A standard, nearly isotropic plasma etch. The plasma contains some ions, which attack the wafer from a nearly vertical direction. Sulfur hexafluoride [SF6] is often used for silicon.

- Deposition of a chemically inert passivation layer. (For instance, Octafluorocyclobutane [C4F8] source gas yields a substance similar to Teflon.)

Each phase lasts for several seconds. The passivation layer protects the entire substrate from further chemical attack and prevents further etching. However, during the etching phase, the directional ions that bombard the substrate attack the passivation layer at the bottom of the trench (but not along the sides). They collide with it and sputter it off, exposing the substrate to the chemical etchant.

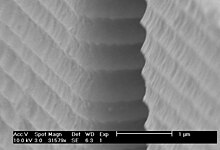

These etch/deposit steps are repeated many times over resulting in a large number of very small isotropic etch steps taking place only at the bottom of the etched pits. To etch through a 0.5 mm silicon wafer, for example, 100–1000 etch/deposit steps are needed. The two-phase process causes the sidewalls to undulate with an amplitude of about 100–500 nm. The cycle time can be adjusted: short cycles yield smoother walls, and long cycles yield a higher etch rate.

Applications

[edit]Etching depth typically depends on the application:

- in DRAM memory circuits, capacitor trenches may be 10–20 μm deep,

- in MEMS, DRIE is used for anything from a few micrometers to 0.5 mm.

- in irregular chip dicing, DRIE is used with a novel hybrid soft/hard mask to achieve sub-millimeter etching to dice silicon dies into lego-like pieces with irregular shapes.[7][8][9]

- in flexible electronics, DRIE is used to make traditional monolithic CMOS devices flexible by reducing the thickness of silicon substrates to few to tens of micrometers.[10][11][12][13][14][15]

DRIE is distinguished from RIE from its etch depth. Practical etch depths for RIE (as used in IC manufacturing) would be limited to around 10 μm at a rate up to 1 μm/min, while DRIE can etch features much greater, up to 600 μm or more with rates up to 20 μm/min or more in some applications.

DRIE of glass requires high plasma power, which makes it difficult to find suitable mask materials for truly deep etching. Polysilicon and nickel are used for 10–50 μm etched depths. In DRIE of polymers, Bosch process with alternating steps of SF6 etching and C4F8 passivation take place. Metal masks can be used, however they are expensive to use since several additional photo and deposition steps are always required. Metal masks are not necessary however on various substrates (Si [up to 800 μm], InP [up to 40 μm] or glass [up to 12 μm]) if using chemically amplified negative resists.

Gallium ion implantation can be used as etch mask in cryo-DRIE. Combined nanofabrication process of focused ion beam and cryo-DRIE was first reported by N Chekurov et al in their article "The fabrication of silicon nanostructures by local gallium implantation and cryogenic deep reactive ion etching".[16]

Precision machinery

[edit]DRIE has enabled the use of silicon mechanical components in high-end wristwatches. According to an engineer at Cartier, “There is no limit to geometric shapes with DRIE,”.[17] With DRIE it is possible to obtain an aspect ratio of 30 or more,[18] meaning that a surface can be etched with a vertical-walled trench 30 times deeper than its width.

This has allowed for silicon components to be substituted for some parts which are usually made of steel, such as the hairspring. Silicon is lighter and harder than steel, which carries benefits but makes the manufacturing process more challenging.

See also

[edit]References

[edit]- ^ Basic Bosch process patent application

- ^ Improved Bosch process patent application

- ^ Bosch process "Parameter Ramping" patent application

- ^ Method of anisotropically etching silicon

- ^ Method for anisotropic etching of silicon

- ^ Method of anisotropic etching of silicon

- ^ Ghoneim, Mohamed; Hussain, Muhammad (1 February 2017). "Highly Manufacturable Deep (Sub-Millimeter) Etching Enabled High Aspect Ratio Complex Geometry Lego-Like Silicon Electronics" (PDF). Small. 13 (16): 1601801. doi:10.1002/smll.201601801. hdl:10754/622865. PMID 28145623.

- ^ Mendis, Lakshini (14 February 2017). "Lego-like Electronics". Nature Middle East. doi:10.1038/nmiddleeast.2017.34.

- ^ Berger, Michael (6 February 2017). "Lego like silicon electronics fabricated with hybrid etching masks". Nanowerk.

- ^ Ghoneim, Mohamed; Alfaraj, Nasir; Torres-Sevilla, Galo; Fahad, Hossain; Hussain, Muhammad (July 2016). "Out-of-Plane Strain Effects on Physically Flexible FinFET CMOS". IEEE Transactions on Electron Devices. 63 (7): 2657–2664. Bibcode:2016ITED...63.2657G. doi:10.1109/ted.2016.2561239. hdl:10754/610712. S2CID 26592108.

- ^ Ghoneim, Mohamed T.; Hussain, Muhammad M. (23 July 2015). "Review on physically flexible nonvolatile memory for internet of everything electronics". Electronics. 4 (3): 424–479. arXiv:1606.08404. doi:10.3390/electronics4030424. S2CID 666307.

- ^ Ghoneim, Mohamed T.; Hussain, Muhammad M. (3 August 2015). "Study of harsh environment operation of flexible ferroelectric memory integrated with PZT and silicon fabric" (PDF). Applied Physics Letters. 107 (5): 052904. Bibcode:2015ApPhL.107e2904G. doi:10.1063/1.4927913. hdl:10754/565819.

- ^ Ghoneim, Mohamed T.; Rojas, Jhonathan P.; Young, Chadwin D.; Bersuker, Gennadi; Hussain, Muhammad M. (26 November 2014). "Electrical Analysis of High Dielectric Constant Insulator and Metal Gate Metal Oxide Semiconductor Capacitors on Flexible Bulk Mono-Crystalline Silicon". IEEE Transactions on Reliability. 64 (2): 579–585. doi:10.1109/TR.2014.2371054. S2CID 11483790.

- ^ Ghoneim, Mohamed T.; Zidan, Mohammed A.; Alnassar, Mohammed Y.; Hanna, Amir N.; Kosel, Jurgen; Salama, Khaled N.; Hussain, Muhammad (15 June 2015). "Flexible Electronics: Thin PZT-Based Ferroelectric Capacitors on Flexible Silicon for Nonvolatile Memory Applications". Advanced Electronic Materials. 1 (6): 1500045. doi:10.1002/aelm.201500045. S2CID 110038210.

- ^ Ghoneim, Mohamed T.; Kutbee, Arwa; Ghodsi, Farzan; Bersuker, G.; Hussain, Muhammad M. (9 June 2014). "Mechanical anomaly impact on metal–oxide–semiconductor capacitors on flexible silicon fabric" (PDF). Applied Physics Letters. 104 (23): 234104. Bibcode:2014ApPhL.104w4104G. doi:10.1063/1.4882647. hdl:10754/552155. S2CID 36842010.

- ^ Chekurov, N; Grigoras, K; et al. (11 February 2009). "The fabrication of silicon nanostructures by local gallium implantation and cryogenic deep reactive ion etching". Nanotechnology. 20 (6): 065307. Bibcode:2009Nanot..20f5307C. doi:10.1088/0957-4484/20/6/065307. PMID 19417383. S2CID 9717001.

- ^ Kolesnikov-Jessop, Sonia (23 November 2012). "Precise Future of Silicon Parts Still Being Debated". The New York Times. New York.

- ^ Yeom, Junghoon; Wu, Yan; Selby, John C.; Shannon, Mark A. (2005). "Maximum achievable aspect ratio in deep reactive ion etching of silicon due to aspect ratio dependent transport and the microloading effect". Journal of Vacuum Science & Technology B: Microelectronics and Nanometer Structures. 23 (6). American Vacuum Society: 2319. Bibcode:2005JVSTB..23.2319Y. doi:10.1116/1.2101678. ISSN 0734-211X.